## MCS6532 DESIGN SPECIFICATION

# This specification contains a detailed description of the MOS Technology, Inc. MCS6552. This document is intended to serve as the basis for internal design work as well as a basis for external specifications, samuels, etc.

# WRITTEN - REVISION A

.

APPROVED - REVISION A

N. L. Mathys Date

E. R. Hirt Date

## MCS6532 DESIGN SPECIFICATION

## CONTENTS

| 1.0   | Introduction             | • | • | • | • | • | •   | •  | •  | ¢ | • | ••• | •    | 3 |

|-------|--------------------------|---|---|---|---|---|-----|----|----|---|---|-----|------|---|

| 2.0   | MCS6532 Pinout           | • | • | • | • | • | •   | •  | •  | ٠ | • | •   | •.   | 4 |

| 3.0   | Internal Organization .  | ٠ | • | • | • | • | • · | ·  | ٠  | • | ٠ | •   | •    | 7 |

| 4.0   | Microprocessor Interface | • | • | • | • | • | •   | •  | •  | · | • | e   | • 1  | 0 |

| 5.0   | Peripheral À Interface . | ٠ | ۲ | • | • | • | •   | ٩  | ٠  | ٠ | • | •   | .2   | 5 |

| 6.0   | Peripheral B Interface . | • | ¢ | • | • | ٠ | •   | ۰. | •  | • | • | ¢   | •?   | 6 |

| 7.0   | RAM Operation            | • | • | • | • | • | •   | •  | •  | • | • | ٠   | .1   | 7 |

| 8.0   | Interval Timer Operation | • |   |   | • | • | •   | •  | •• | • | • | e   | •1   | 8 |

| . 8.0 | Programming the MCS6532  | · | · | • |   | • | •   | •  | •  | • | • | •   | .2   | 1 |

| 10.0  | D.C. Specifications      |   | • | ٠ | • | • | ,   | ٠  | •  | ٠ | • | •   | • •2 | 3 |

| 11.0  | AC Specifications        | • | ٠ | • | • | • | •   | •  | •  | • | • | •   | •3   | 0 |

|       |                          |   |   |   |   |   |     |    |    |   |   |     |      |   |

## MCS6532 DESIGN SPECIFIC/TION

1.0 Introduction

The MCS6532 is a multiple-function microprocessor support chip containing 128 bytes of RAM, sinteen I/O pins, an interval timer and an edge-sensitive interrupt input. It is designed to allow maximum flexibility in the implementation of systems which use the MCS6500 microcomputer components.

Some important features of the MCS6532 are:

- \* & bit bi-directional Data Bus for communication with the microprocessor

- \* Edge Sense Interrupt (Positive or Negative Edge Programmable)

- \* 128 x 8 static RAM

- \* Two C bit bi-directional deta ports for interface to peripherals

- \* Two programmable Peripheral Data Direction Registers

- \* Programmable Interval Timer

- \* TTL & CHOS comparible peripheral lines

- \* Peripheral pins with Direct Transistor Drive Capability

- \* High Impedance Three-State Data Bus

2.0 MCS6532 Pinouts

2.0 BUSDESSETTIMOUTS Figure 2.1 shows the pin configuration for the MCS6532. These pins are described briefly in this section. A detailed description of the operation, and a specification of all AC and DC characteristics for these pins, is contained in subsequent sections.

. •

| rin #        | PIH NAUS       | DESCRIPTION                                                                                    |

|--------------|----------------|------------------------------------------------------------------------------------------------|

| 1, 20        | VSS, GND       | Chip power supply connections.                                                                 |

| 2~7, 40      | Аф-Аб          | Address Inputs - Allow selection of<br>the various RAM and I/O registers on<br>the chip.       |

| 8-15         | <b>РАФ</b> РА7 | Peripheral A I/O port. Eight-bit<br>general-purpose bi-directional data<br>port.               |

| 16-19, 21-24 | Рвф-Рв7        | Periphoral B 1/0 port. Eight-bit<br>general-purpose bi-directional data<br>port.               |

| 25           | •              | Interrupt Request Output. Goes to<br>the processor Hig or will input to<br>allow interrupting. |

| 2633         | DBØDB7         | Bata Bus - Allows transfer of 8 bit<br>bytes of data between the processor<br>and the MCS6532. |

| 34           | RES            | Reset - Clears all internal registers to zeros.                                                |

| 35           | R/W            | Read/Mrite control from processor.                                                             |

| 36           | RS             | RAM Select input.                                                                              |

| 37, 38       | CS1, CS2       | Chip Select inputs.                                                                            |

| 39           | <b>\$</b> 2    | Phase Two system clock input.                                                                  |

|              |                |                                                                                                |

| (cup)        | MOS          | -6532 |     |

|--------------|--------------|-------|-----|

| (GND)<br>VSS | EIC          | 40    | A6  |

| A5           | <b>[</b> ] 2 | 39    | Ø2  |

| A4           | T 3          | 38 ]  | CS1 |

| A3           | 1            | 37    | CS2 |

| A2.          | 5            | 36    | RS  |

| A1           | <b></b>      | 35    | R/W |

| Aø           | 二 7          | 34    | RES |

| PAØ          | E 8          | 33    | DBØ |

| PA1          | 19           | 32 ]] | DBY |

| PA2          | 10           | 31    | DB2 |

| .PA3         | 11           | 30    | 083 |

| PA4          | E-11.2       | 2: ]  | DB4 |

| PA5          | [_])3        | 28    | DB5 |

| PAG          | C14          | 27 _1 | DB6 |

| PA7          | 1.5          | 26    | DB7 |

| PB7          | E-126        | 25    | IRQ |

| P86          | 17           | 24    | P₿Ø |

| PB5          | 1=13         | 23    | PB1 |

| PB4          | []19         | 22    | PBZ |

| VDD          | 120          | 21    | PB3 |

|              | 1            |       |     |

Figure 2.1 MCS 6532 PIN DESIGNATION

3.0 Internal Organization of the MCS6532

#### 3.1 Introduction

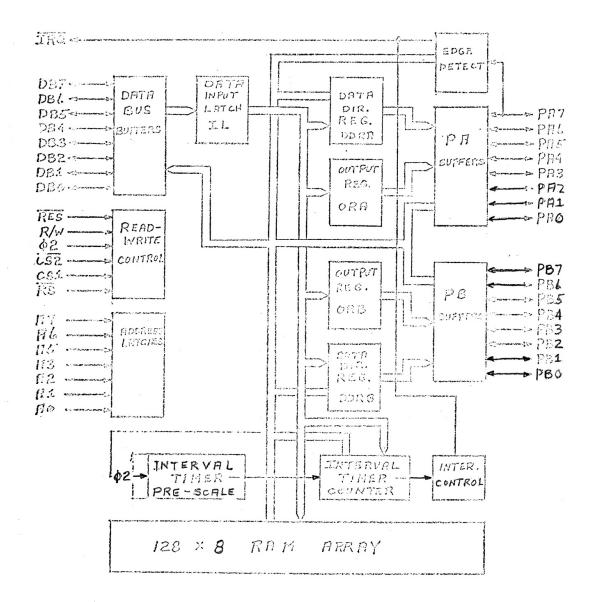

Figure 3.1 contains a block diagram of the MCS6532 showing the various data paths, registers, buffers, etc. on the chip. These logic blocks are described in this section in sufficient detail to serve as a basis for the specifications contained in Sections 4.0, 5.0 and 6.0.

## 3.2 Data Bus Buffers

The buffers which drive the system data bus are push-pull devices which remain in the high-impedance state except when the MCS6532 is transferring data to the system processor. In the output mode, they are capable of driving one standard TTL device and up to ten MCS6500 family devices. In the input mode, the data bus pins represent primarily a capacitive load to the other devices in the system since the output drivers go to a high-impedance state.

## 3.5 Deta Input Latch

All data being transferred into the MC56552 is first stored in the Data Input Latch. This is necessary in any 1/0device to avoid "glitching" the peripheral output pins. The deta is latched into the Input Latch during the Phase Two system clock pulse. From there it is transferred into the internal registers (RAM, EDDA, etc.) during the next Phase Two (G2=0.4V) system clock pulse. This allows the peripheral interface output pins to remain stable except when they are going to reverse polarity.

## 3.4 Read/Write Control

The Read/Write control logic responds to address inputs, chip select inputs, the R/W line and the clock input to control data transfers between the MCS6532 registers and the system data bus.

## 3.5 Address Latches

Since the data being transferred into the MCS6532 is first stored in the input latch and is transferred internally during the next Phase Two, it is necessary to latch the chip select and address inputs. The Address Latches store the addresses generated by the processor, latching the addresses on the leading edge of Phase Two. These addresses are then used to control the transfer of data from the Data lnput Latch to the various registers on the chip.

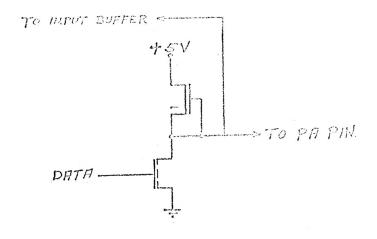

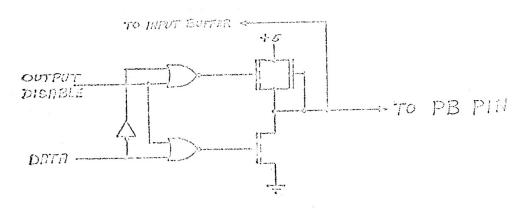

PERIPHERAL A PORT BUFFER

FIGURE 3.2. MCS6532 PERIPHERAL BUFFERS

## 3.6 RAM Array

The Read/Write memory array can store up to 128 eight-bit bytes of data which can be written into the RAM by the system microprodessor. By providing the proper address and chip select signals, the processor can read the data at any time.

## 3.7 Peripheral Buffers

The peripheral buffers provide the voltage and current necessary for controlling peripheral devices. On the Peripheral A Port, the active pull-ups are always on and are always connected to the peripheral pin. For this reason, these pins represent one standard TTL load in the input mode. In the output mode, the buffers on both the PA and PB ports are capable of driving one standard 'TL load. In addition, the PB buffers are capable of sourcing 3 ma at 1.5 VDC. This allows these pins to directly drive Barlington transistors.

Both the PA and the PB ports are capable of generating the voltage levels necessary to drive CMOS. However, the depletionmode pull-up device which makes this possible causes both the PA and PB ports to source current in the input mode.

Figure 3.2 contains a logic diagram of the PA and PB Buffers.

## 3.3 Pats Direction Registers

The PA and PB peripheral ports each consist of eight lines which can be individually programmed to act as either an input or an output. This input/output configuration is determined by the Data Direction Register. Setting a "0" into a bit of the Data Direction Register causes the corresponding peripheral pin to act as an input. A "1" causes the peripheral to act as an output.

## 3.9 Output Registers

As discussed in the provious section, the peripheral pins can be programmed to act as either an input or an output. In the output mode, the voltage on the peripheral pin is controlled by the corresponding bit of the Output Register. A " $\mathcal{G}$ " in Output Register causes the corresponding peripheral output line to go low (0.4V). A "1" causes the peripheral output line to go high (+SV).

## 3.10 Edge Detect Logic

In addition to acting as a peripheral 1/0 pin, PA7 can also act as an edge sensitive interrupt input. Any active transition of the signal on PA7 will set the internal interrupt flag. If the interrupt is enabled, the IRQ output will go low when the interrupt flag is set.

## 4.0 Microprocessor Interface

The interface between the MCS6532 and the system microprocessor contains signals for transferring data (DBØ-DB7), for controlling the direction and timing of these transfers (R/W,  $\beta$ 2), for addressing the various on-chip registers ( $A\beta$ -A6, RS, CS1, CS2), for resetting the chip (RES) and for allowing the MCS(532 to interrupt the microprocessor (IRQ). The operation of each of these is described in detail in this section.

## 4.1 Resetting the MCS6532

All of the registers on the MCS6532 (excluding the RAM) can be reset to logic zero by placing a low (0.4V) on the RES input. This is normally accomplished by a meeting this input to the system reset signal. As 1c is RES is low, all peripheral I/O pins will be set to the uput state and all interrupts will be disabled. Causing the to go high will allow all normal chip operations to be:

4.2 Interrupting the Microprocessor

The MUS6532 can interrupt the miniprocessor as a result of an active transition on the edge-relative input on from a time-out of the interval timer. Elter of these conditions can cause the IM output to go low to deterrupt the processor. This IRO cutuat is "open-drain", i.e. it has no rull-up device. This allows this signal to be "wire-orded" with similar signals from other peripheral interface devices in the system.

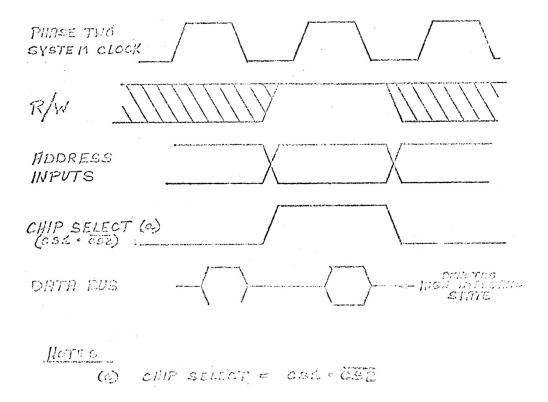

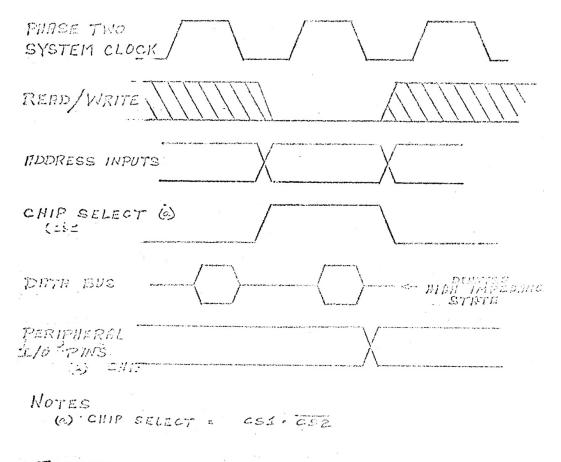

4.3 Reading the MCS6552

Bata can be transferred from the MCS6532 into the system microprocessor by placing a logic 1 on the P/W line, selecting the chip (CS1=1, CS2=0) and placing the address of the desired data on the address inputs (AØ-Aô, RS). The desired data will then be placed on the Data Bus during the Phase Two system clock pulse ( $\beta$ 2=2.4V). This timing sequence is shown in Pigure 4.1.

Selection of the various 1/0 ports, registers and RMM bytes is accomplished by connecting the microprocessor address outputs to the RAM Select input (RS), the chip select inputs (CS1, CS2) and the address inputs (AP-A6). The RUM is selected by placing a low (0.4V) on RS and selecting the chip. The address inputs (AP-A6) can then be used to select one of the 123 bytes of memory in the RAM section. With the RS input high and the chip selected (CS1=2.4V, CS2=0.4V), the address inputs can be used to address the various I/O registers as shown in Figure 4.2.

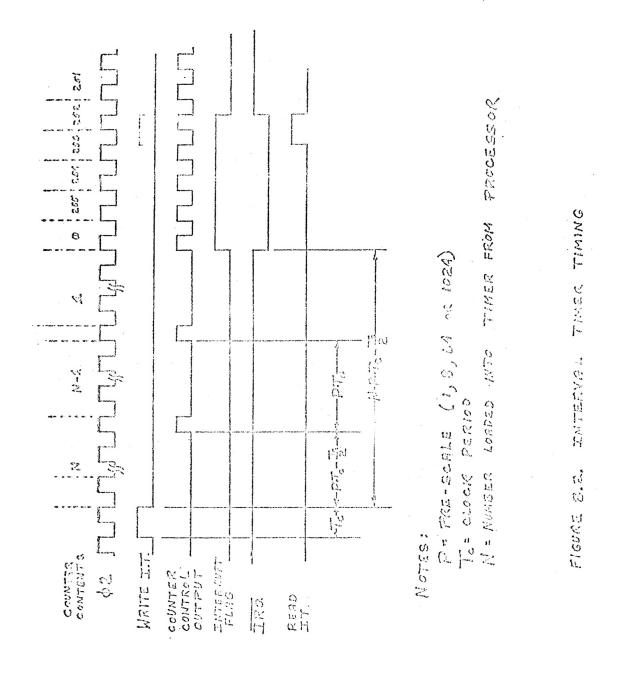

4.4 Writing the MCS6532 Writing from the microprocessor into the MCS6532 registers, RAM memory, etc. is accomplished in much the same manner as that described in the previous section for reading. However, the R/W line must go low to cause the transfer of data into the chip. With the chip selected, and R/W=0.4V, the data on the Data Bus will be transferred into the input latch and then into the selected I/O register or RAM memory location. This timing sequence is shown in Figure 4.3. As shown in Figure 4.2, addressing of the I/O registers operates somewhat differently for reading and writing.

FIGURE 4.1. Mas 6532 READ SEQUENCE

|                                 | RS | R/W    | A4 | K3     | A2 | 11       | ζλ  |

|---------------------------------|----|--------|----|--------|----|----------|-----|

| Read PA Pins                    | 1  | 1      | х  | X.     | 0  | 0        | 0   |

| Write Output Register A         | 1  | 0      | Х  | Х      | 0  | 0        | 0   |

| Read Data Direction Register A  | 2  | 3      | х  | X      | 0  | 0        | 3.  |

| Write Data Direction Register A | 1  | 0      | х  | Х      | 0  | 0        | ]   |

| Read Output Register B          | 1  | 1      | Х  | Х      | 0  | 3.       | 0   |

| Write Output Register B         | 1  | 0      | х  | Х      | 0  | 1        | 0   |

| Read Data Direction Register B  | 1  | )      | X  | χ      | 0  | 1        | 1   |

| Write Data Direction Register B | 1  | 0      | Х  | Х      | 0. | )        | 1   |

| Read Interval Timer             | 1  | 1      | ·x | (b)    | 1  | Х        | 0   |

| W-ite Interval Timer            |    | •      |    |        |    |          |     |

| a l                             | 1  | . 0    | 1  | (b)    | 1  | 0        | 0   |

| 4 C                             | Ŷ  | õ      | 2  | (b)    | 1  | 0        | 1   |

| * 04                            | ĩ  | 0      | ĩ  | (b)    | ĩ  | 1        | 0   |

| ♣ 04<br>♣ 1024                  | 1  | 0      | 1  | (b)    | 1  | 1        | 1   |

|                                 | 2  | 1      | Y  | X      | 1  | <u>y</u> | 3   |

| Read Interrupt Flags            |    | n<br>1 | 0  | x<br>x | 1  | (c)      | (3) |

| Mrite Edge Detect Control       | 1  | 0      | U  | 44     | 4  |          | (0) |

|                                 |    |        |    |        |    |          |     |

NOTES:

.

•

| (a)         | X = Denit Core                               |

|-------------|----------------------------------------------|

| (6)         | A3 = \$, Disable Interrupt to IRQ from Timor |

|             | A3 = 1, Enable Interrupt to 180 from Timer   |

| ()          | Al = 6, Disable Interrupt to IRQ from PA7    |

|             | Al = 1, Enable Interrupt to IAQ from PA7     |

| (5)         | AØ = Ø, Negative Edge Detect                 |

|             | AØ = 1, Positive Edge Patent                 |

| (0)         | Ø = 0.4V                                     |

|             | 1 = 2.4 V                                    |

| <b>(</b> £) | $CS1 = 1, CS2 = \emptyset$                   |

|             |                                              |

| Ø i         | 7 = flag goes high on interval time-out      |

| Dit         | - study you and a stransition                |

| Bit         | 6 = flag goes high on active transition      |

| CIL         | ·                                            |

Figure 4.2 Addressing the MCS6552 Registers

FIGURE 4.3. MCS6532 WRITE SEQUENCE

## 5.0 Peripheral A Interface

The Peripheral A I/O port consists of eight lines which can be individually programmed to act as either an input or an output. A logic zero in a bit of the Data Direction Register (DDRA) causes the corresponding line of the PA port to act as an input. A logic one causes the corresponding PA line to act as an output. The voltage on any line programmed to be an output is determined by the corresponding bit in the Output Register (ORA).

Deta is read directly from the PA pins during any read operation. For any output pin, the data transferred into the processor will be the same as that contained in the Output Register if the voltage on the pin is allowed to go to 2.4V for a logic one. Note that for input lines, the processor can write into the corresponding bit of the Output Register. This will not effect the polarity on the pin until the corresponding bit of DDRA is set to a logic one to allow the peripheral pin to act as an output.

Figure 4.3 shows the timing sequence for writing the Peripheral port. Note that the outputs change on Phase Two (Phase Two=0.4V) as discussed in Section 3.3.

In addition to acting as a peripheral 1/0 line, the PAV line can be used as an edge-detecting input. In this mode, an active transition will set the internal interrupt flag (bit 6 of the Interrupt Flag register). Secting the interrupt flag will cause IRQ output to go low if the PAT interrupt has been enabled.

Control of the PA7 edge detecting mode is accomplished by writing to one of four address. In this operation, Af controls the polarity of the active transition and Al acts to enable or disable interrupting of the processor. The data which is placed on the Data Bus during this operation is discarded and has no effect on the control of PA7.

Setting of the PA7 active transition if the pin is being used os a normal input or as a peripheral control output. The flag will also be set by an active transition if interrupting from PA7 is disabled. The reset signal (NES) will disable the PA7 interrupt and will set the active transition to negative (high to low). During the system initialization routine, it is possible to set the interrupt fleg by a negative transition. It may also be set by changing the polarity of the active interrupt. It is therefore recommended that the interrupt flag be cleared before enabling interrupting from PA7.

Clearing of the PA7 Interrupt Flag occurs when the microprocestor reads the Interrupt Flag Register as shown in Figure 4.2.

6.0 Peripheral E Interface

The operation of the Peripheral B Input/Output port is exactly the same as the normal 1/O operation of the Peripheral A port. The eight lines can each be programmed to act as either an input or as an output by placing a 9 or a 1 into the Data Direction register (DDRS). In the output mode, the voltage on a peripheral pin in controlled by the Output Register (ORB).

The primary difference between the PA and the PB ports is in the operation of the output buffers which drive these pins. As shown in Figure 3.2, the buffers are push-pull devices which are capable of sourcing 3 ma at 15 volts. This allows these pins to directly drive transistor switches. To assure that the microprocessor will read proper data on a "Read PB" operation, sufficient logic is provided in the chip to allow the microprocessor to read the Output Register instead of reading the peripheral pin as on the PA port. The AC and DC specifications for the PB port are contained in Sections 10.0 and 11.0.

7.0 RAM Operation The J28 x 8 Read/Write memory acts as a conventional static RAM. Data can be written into the RAM from the microprocessor by selecting the chip (CS1=1, C52= $\emptyset$ ) and by setting RS to a logic  $\emptyset$  (0.4V). Address lines A $\emptyset$  through A6 are then used to select the desired byte of storage. The timing for the Read and Write operations is specified in detail in Sections 10.0 and 11.0.

## 8.0 Interval Timer Operation

#### 8.1 Introduction

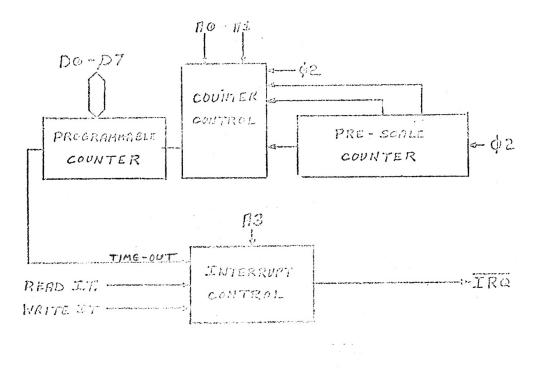

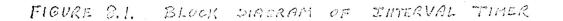

The interval timer in the MCS6532 is a duplicate of that provided on the MCS6530. This counter is divided into two sections; a pre-scale counter and a programmable counter. In addition, the interval timer has interrupt and control logic which determines the operating modes in the timer. Figure 8.1 shows a detailed block diagram of the Interval Timer.

## 8.2 Pre-scale Counter

The 10 bit pre-scale counter generates a pulse every 1, 8, 64 or 1024 system clock pulses. The pulses from the pre-scale are then counted in the programmable counter. Selection of this pre-scale frequency is controlled by varying the address used when writing into the programmable counter. The four addresses which can be used when writing into the interval timer are shown in Figure 4.2 along with the associated pre-scale frequency.

## 8.3 Programmable Counter

The programmable portion of the Interval Timer consists of an eight-bit decrementing counter. This counter can be preset to any desired number by writing from the microprocessor into one of the eight addresses assigned to the counter. The address selected will determine the pre-scale counter output frequency and, in addition, will control the IRQ output.

Immediately after the write operation is complete, the counter will begin to decrement at a frequency determined by the selected pre-scale. When the programmable portion of the interval timer decrements to zero, the interrupt flag will be set. On the next \$2,the IRQ output will go low if the interrupt was enabled during the Timer Write operation (AS=1). At this time the counter will begin to decrement at the system clock rate. This allows the processor to read the counter to determine the "time since interrupt" to a maximum of 255 clock cycles.

The status of the interval timer flag can be determined by reading bit 7 in the Interrupt Flag Register. A logic 1 indicates that the flag is set by a time-out. A logic  $\beta$  indicates that the flag has been cleared.

Figure 8.2 shows the timing sequence which takes place in the MCS6532 interval timer.

#### 9.0 Programming the MCS6532

## S.1 Introduction

There are several very important considerations in the programming of the MCS6532 Interval Timer, and edge-detecting imputs. These are discussed in detail in this section.

9.2 Identification of the MCS6532 Registers for the Assembler.

Because several very important operations in the MCS6532 are controlled by varying addresses, it is usually recommended that each of these addresses be given a separate and meaningful label at the beginning of the program. This will minimize the probability of errors in the text of the program. This can be accomplished very effectively as shown in Figure 9.1.

## 9.3 Programming the Interval Timer

As described in Section 8, the interval timer can be operated either through the processor interrupt or by polling the interrupt flag to detect the time-out. Each of these modes is discussed separately below.

#### 9.3.1 Polled Interval Timer Operation

Operation of the interval timer in the polled mode requires that the processor first load the timer for the proper time-out period. The processor then goes into a software loop in which the timer flog is constantly tested. This sequence is shown in Figure 9.2. In the example shown, a peripheral output is set low for a period determined by the timer.

**9.3.2** Operation of the Timer through the Processor Interrupt By using the proper address during the Timer Write operation, the INQ output can be used to signal the processor that a time-out has occurred. In this operation, the timer is londed with the proper data during execution of the main-line program and the Interrupt Service routine is used to respond to the timecut. This operation is shown in Figure 9.3. In this example a peripheral output is set low for a period of time determined by the interval timer.

Note that the interrupt service routine contains the instructions necessary to disable subsequent interrupts from the timer. This is necessary in any operation where only a single timer interrupt is desired. Figure 9.4 shows a similar example where the timer is used to generate a square wave on a peripheral pin. In this mode, the timer is re-loaded during the interrupt service routine to enable generation of the next interrupt in the sequence.

9.4 Correction of the Time-Out Period

Very accurate time periods can be generated by a microprocessor using the interval timer if the necessary software is proyided to take advantage of the "time-since-interrupt" feature of the MCS6532 interval timer. After a time-out has occurred, the interval timer will continue to decrement at the system clock rate. The "time-since-interrupt" can then be determined by reading the contents of the timer counter. This data can then be used to adjust the next time-out to maintain very accurate overall frequency. Figure 9.5 contains an example of a program which generates pulses which are very accurate in frequency. Missing pages with assembler listing 23-26

| LINE         | ⇔ LUC          | CODE | LINE                                                              |

|--------------|----------------|------|-------------------------------------------------------------------|

| 0001         | 0000           |      | < =\$80000<br>ADAT32 ~=<+1 PA DUTPUT REG                          |

| 0002<br>0003 | 11000<br>11001 |      | ADIRSE *=**1 PA DATA DIR REG                                      |

| 0004<br>0005 | 8002<br>8003   |      | PDATS2 *=**1 PB DUTPUT REG<br>BNURS2 *=**1 PB DATA DIR REG        |

| 0005<br>0007 | A004<br>8004   |      | RITDRE =* READ INT TIMER<br>EDHDRE *=*+1 EDGE BET-NE5 DIS         |

| 8000<br>0000 | A005<br>A005   |      | EDPD32 =* EDGE DET-POS DIS<br>RDIF32 *=*+1 READ INT FLAG          |

| 0010         | 0605<br>0007   |      | EDMESS *=**1 SDGE IET-NEG EN<br>EDMESS *=**13 EDGE DET-PDS EN     |

| 0012         | 8014<br>8015   |      | ITIDS2 <=<+1 T-DIV 1;NO INT<br>IT8D32 <=<+1 I T-DIV 8;NO INT      |

| 0014         | R016<br>8017   |      | IT6D32 *=*+1 I T-DIV 64,NO INT<br>ITKD32 *=*+5 IT-DIV 1024,NO INT |

| 0016         | ROIC           |      | ITIES2 *=*+1 IT-DIV *INT EN<br>IT8E32 *=*+1 IT-DIV 64,INT EN      |

| 0018<br>0019 | A012<br>A01F   |      | TIGES2 +=++1 IT-DIV 64, INT EN<br>TKU32 +=++1 IT-DIV 1024, INT EN |

| 0020         | 0.301          |      | . END                                                             |

· .

.

ERRERS = 0000 WARHINGS = 0000

SYMBOL VALUE

| SSTRUA  |   | A000 |

|---------|---|------|

| FID1R32 |   | R001 |

| DEALSS  |   | 8008 |

| BD1835  |   | 8003 |

| RITDSE  |   | 9004 |

| EDND32  |   | 8004 |

| ENPD32  |   | 8005 |

| RD1F32  |   | A005 |

| EDNE32  |   | 8006 |

| EDPE32  |   | 8007 |

| 111032  |   | R014 |

| JTSD32  | ÷ | 8015 |

| IT6D32  |   | A016 |

| )TKD32  |   | 8017 |

| 1T1ESS  |   | ñ010 |

| ITSE32  |   | A019 |

| 116535  |   | RULE |

| ITKESS  |   | 801F |

|         |   |      |

END DF ASSEMBLY

10.0 D.C. Specifications

This section contains the static operating voltages and currents for the MCS6532. These specifications shall apply over the operating temperature range of 25°C unless otherwise noted.

10:1 Maximum Ratings

| PATING                      | SYMBOL.  | VOLTAGE     | UNIT |

|-----------------------------|----------|-------------|------|

| Supply Voltage              | VCC      | 3 to +7.0   | ۷.   |

| Input/Output Voltage        | $v_{IN}$ | 3 to +7.0   | v    |

| Operating Temperature Range | TOP      | 0 to 70     | oC   |

| Storage Temperature Range   | TSTC     | -55 to +150 | oC   |

All inputs contain protection circuitry to prevent decage due to high static charges. Care should be exercised to prevent unnecessary application of voltage outside the specification range.

## 10.2 Static Operating Characteristics

ELECTRICAL CHARACTERISTICS (VCC = 5.0V ± 5%, VSS - 0V

| MACTERISTIC                                                                                             | SYMBOL                      | HIN                              | TYP          | MAX      | UNIT                   |

|---------------------------------------------------------------------------------------------------------|-----------------------------|----------------------------------|--------------|----------|------------------------|

| put High Voltage                                                                                        | VIH                         | VSS + 2.4                        |              | VCC      | V.                     |

| THE LOW VOLCESS                                                                                         | Y31.                        | Vss3                             |              | VSS + .4 | V.                     |

| put Leekage Current; VIN = 0 to 5V<br>AØ-A6, RS, R/W, RESET, Ø2, CS1, CS2                               | 1 <sub>IN</sub>             |                                  | 1.0          | 2.5      | <b>u</b> A             |

| put Leakage Current for High Impedence State (Three State); $V_{\rm IN}$ = .4V to 2.4V; DB $\beta$ -DB7 | ITSI                        |                                  | <u>+1</u> .0 | +10.0    | uA                     |

| put High Current; VIN = 2.4V<br>PAG-PAT, PDG-PB7                                                        | X)II                        | -200.                            | -300         |          | υA                     |

| inut low Curvent; Vig = .47<br>1965-PA7, 150-1887                                                       |                             |                                  | •1.0         | -1.6     | 113                    |

| ppet Voltage Low<br>VCC = MLC, ILOND - 1.6 mc                                                           |                             |                                  |              |          |                        |

| put High Voltege<br>VCC = NIN, JLOAD 100uA<br>JLOAD 3 MA PDØ-137                                        | V <sub>CII</sub>            | $V_{SS} + 2.4$<br>$V_{SS} + 1.5$ |              |          |                        |

| Nog - 2.4V<br>Yog - 2.4V<br>- 1.5V Available for other than TTL<br>(Tarlingtons)                        | Y <sub>ON</sub>             | -100<br>-3.0                     | -1000        |          | ил<br>Ма               |

| stput Low Current (Sinking); VOL .4V                                                                    | 1 <sub>0)</sub> ,           | 1.6                              |              |          | МА                     |

| . ock Imput Capacitaneo                                                                                 | $\mathbf{c}_{\mathrm{CLX}}$ |                                  |              | 30       | pf                     |

| aput Capacitonce                                                                                        | $\mathbf{c}_{\mathrm{IN}}$  |                                  |              | 10       | $\mathbf{pf}$          |

| : tput Copecitonce                                                                                      | com                         |                                  |              | 30       | $\mathbf{b}\mathbf{b}$ |

| wer dissipation                                                                                         | $P_{D}$                     |                                  | 500          | 1000     | 164                    |

11 values are D.C. readings.

## 11.0 A.C. Specifications

This section contains the dynamic operating characteris-tics for the MCS6532. These specifications apply at 25°C unless otherwise noted.

11.1 Read Operation Figure 11.1 shows the timing sequence for the MCS6532 Read operation. This figure also identifies the dynamic para-meters which will be specified in this section.

## The limits for these parameters are:

| CHARACTERISTIC                                                              | SYMBOI, | MIN  | TYP | МАХ | UNIT |

|-----------------------------------------------------------------------------|---------|------|-----|-----|------|

| P/W valid before positive transition of clock                               | TWCR    | 1.80 |     |     | NS   |

| Address valid before positive transition of clock                           | TACR    | 180  |     |     | NS   |

| Forigheral data valid before positive transition of clock                   | TPCR    | 300  |     |     | ЮS   |

| Deta fus valid after positive transition of clock                           | TCDR    |      |     | 505 | 115  |

| Data bus Hold Time                                                          | THE     | 10   |     |     | NS   |

| )KQ (Interval Timer Interrupt) valid before<br>positive transition of clock | TIC     | 200  |     |     | NS   |

Loading = 30 pf + TTL load for PAS-PA7, PES-PE7

=130 pf + 1 TTL locd for DJ-D7

11.3 Write Operation Figure 11.2 shows the timing sequence for a MCS6532 Write operation. This figure also identifies the dynamic parameters which will be specified in this section.

| CHARACTERISTIC                                                                             | SYMBOL | MIN  | TYP | MNX | UNIT |  |

|--------------------------------------------------------------------------------------------|--------|------|-----|-----|------|--|

| Clock Period                                                                               | TCYC   | 1    |     |     | uS   |  |

| Rise & Fall Times                                                                          | TR, TF |      | 1.  | 25  | NS   |  |

| Clos. Pulse Width                                                                          | TC     | \$70 |     |     | NS.  |  |

| R/W valid before positive transition of clock                                              | THCW   | 180  |     |     | NS   |  |

| Address valid before positive transition of clock                                          | TACH   | 180  |     |     | RS   |  |

| Pata hus valid before negative transition of clock                                         | TEAN   | 360  |     |     | RS   |  |

| Lata Eus Hold Time                                                                         | 71117  | 10   |     |     | ns   |  |

| Peripherol Data valid after negative transition of clock                                   | YCTH   |      |     | λ   | r5   |  |

| Peripheral Data valid after negative transition<br>of clock driving CNOS (Level = VCC-30%) | TCHOS  |      |     | 2   | vS   |  |

|                                                                                            |        |      |     |     |      |  |

11.3 Write Operation Figure 11.2 shows the timing sequence for a MCS6532 Write operation. This figure also identifies the dynamic parameters which will be specified in this section.

| CHARACTERISTIC                                                                             | SYMBOL               | MIN        | TYP | MAX | UNIT           |

|--------------------------------------------------------------------------------------------|----------------------|------------|-----|-----|----------------|

| Clock Period                                                                               | TCYC                 | 1          |     |     | uS             |

| Rise & Fall Times<br>Clock Pulse Width<br>R/W valid before positive transition of clock    | TR, TF<br>TC<br>TMCW | 470<br>180 |     | 25  | ns<br>NS<br>NS |

| Address valid before positive transition of clock                                          | TACM                 | 180        |     |     | NS             |

| Data hus valid before negative transition of clock                                         | TECH                 | 300        |     |     | KS             |

| Data fus Hold Time                                                                         | 71117                | 10         |     |     | ns             |

| Peripheral Data valid after negative transition of clock                                   | TCFN                 |            |     | J   | 15             |

| Peripheral Data valid after negative transition<br>of clock driving CNOS (Level = VCC-30%) | TCMOS                |            |     | 2   | vS             |